反射是引起SI的一個最基本因素,信號在傳輸線傳播過程中,一旦它所感受到的傳輸線瞬時阻抗發生變化,那么就必將有發射發生;反射是由于傳輸線瞬時阻抗變化而引起的。

下面就從理論角度來分析一下反射的機理、反射系數和傳輸系數的計算,配個簡易圖來加以說明

圖中褐色的為電路板上的大面積鋪銅層(GND或者PWR),它是信號的返回路徑。綠色和紅色是傳輸線,S1比較寬,S2較窄,很明顯在S1和S2的交接處出現了阻抗不連續,根據阻抗計算公式應該是Rs1<Rs2

那么究竟有多少信號被反射了呢?又有多少信號通過了界面進入S2了呢?

這里就涉及到了反射的計算,即反射系數的計算和傳輸系數的計算;在交界面,雖然阻抗發生了變化,但是電壓和電流一定都是連續的這個結論一定要能理解,電壓和電流不可能出現一個斷裂即在交界面的左邊一點和右邊一點,他們的電壓和電流都是相等的這里的一點點就像微積分中的那么一小點

在分界面的左邊一點點S1中有:Rs1=V1/I1 (1)

在分界面的右邊一點點S2中有:Rs2=V2/I2 (2)

其中的V1、V2分別為分界面兩側的電壓,I1和I2為分界面兩側的電壓

由上面的電壓和電流連續性得知:V1=V2,I1=I2 (3)

分析上面的三組方程,如果沒有反射,他們是不可能同時成立的

因為Rs1和Rs2是不相等的所以可以判定在分界面必定存在反射回源端的信號,反射電壓設為Vf,反射電流為If,進入S2的電壓為Vt,電流為It(稱他們為傳輸電壓和傳輸電流)

信號電壓為Vi,電流為Ii(稱之為輸入電壓,從分界面看)

電壓關系有:Vi+Vf=Vt

電流關系有:Ii-If=It

這又是很關鍵的兩個關系式

因為Vi/Ii=Rs1

Vf/If=Rs1

Vt/It=Rs2

把這三個關系式代入到上面的兩個電壓和電流關系方程中可以得到

Vi/Rs1-Vf/Rs1=Vt/Rs2=(Vi+Vf)/Rs2

(Vi-Vf)/Rs1=(Vi+Vf)/Rs2

反射系數X定義為反射電壓和輸入電壓的比值,即Vf/Vi,可求的X=(Rs2-Rs1)/(Rs1+Rs2)

傳輸系數Y定義為傳輸電壓和輸入電壓的比值,即Vt/Vi,經過X式小變形即可求得:Y=2Rs2/(Rs1+Rs2)

反射是經常遇到的SI問題,我們只能無限地縮小它,卻不能完全消除它,在波形能夠接受的情況下盡量做到最大限度的抑制反射,這就是我們要做的工作。

最重要的就是匹配電阻的阻值確定,匹配的端接確定即采用何種匹配。源端串接和接收端并接的匹配方式是不一樣的。

反射系數,即X=(Z2-Z1)/(Z1+Z2),Z1和Z2分別為傳輸線阻抗失配分界面前后的瞬時阻抗。

那么這就有3種情況:

1.Z1=Z2,即阻抗相等,X=0,即沒有反射

2.Z2=無窮大,X=1,即完全正反射,很多接收端的情況

3.Z2=0,X=-1,即完全負反射,末端短路了,接地了,阻抗為0,反射信號即可以理解為返回路徑上的回流源端串聯電阻R,和驅動端的源電阻R0,串聯后的總電阻R+R0,總電阻值等于或者最接近傳輸線阻抗Z。那么這時候信號分壓,真正進入傳輸線上傳播的只有源信號電壓的一半,到接收端時,由于接收端阻抗為無窮大,發生反射,反射系數為1,傳輸系數Y=2,即進入接收端的信號又等于驅動端的信號了。而返回源端的信號因為阻抗沒有變化,到源端時被源電阻和串聯匹配電阻吸收了,不再發生反射,這是理想情況。究竟多大的反射才會引起我們的注意呢?什么樣的情況下才需要作阻抗匹配呢?下面就來探討一下:

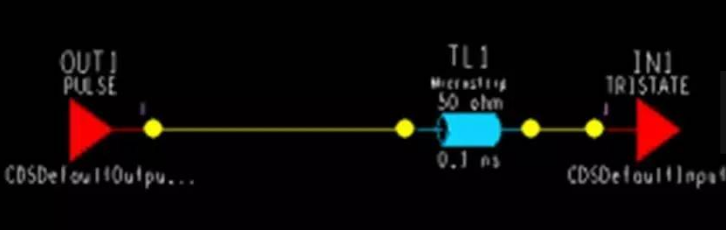

我們在SigXplorer中搭建一個簡易的Point-Point拓撲結構,開始時對驅動端的源電阻不得而知,使用理想傳輸線,特征阻抗為50ohm,傳輸延時為0.1ns,未加任何阻抗匹配元件,仿真頻率選擇50Mhz。

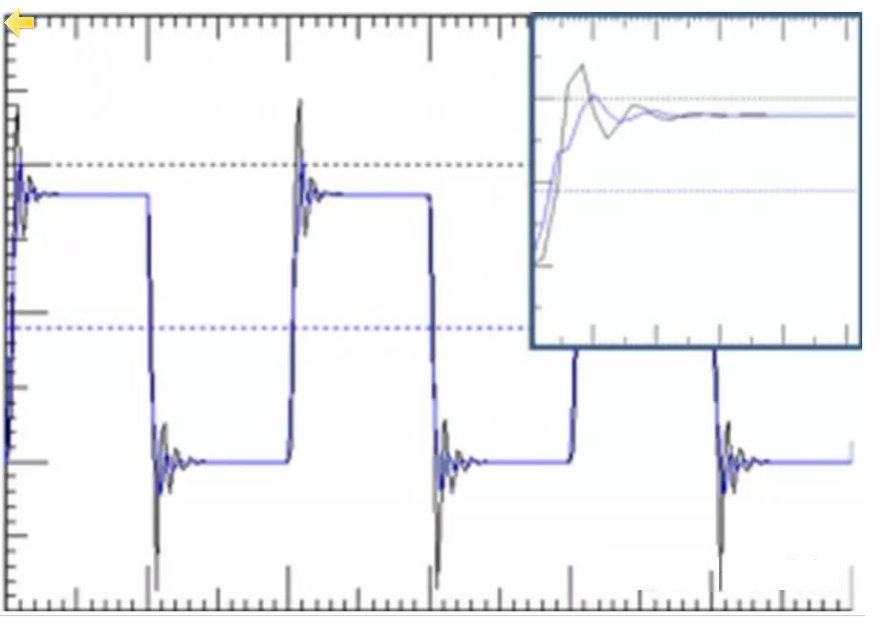

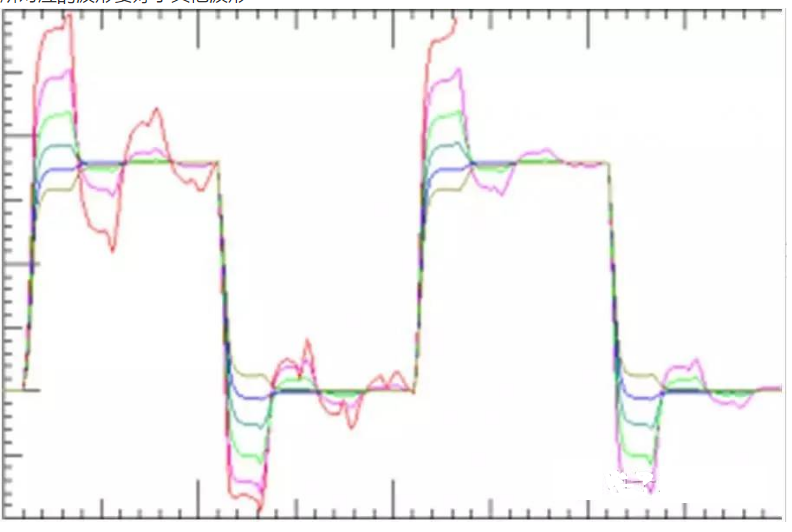

下面來看一下仿真波形,從圖示中的放大部分可以看到驅動端和源端都有明顯的振鈴存在,并且過沖比較大。

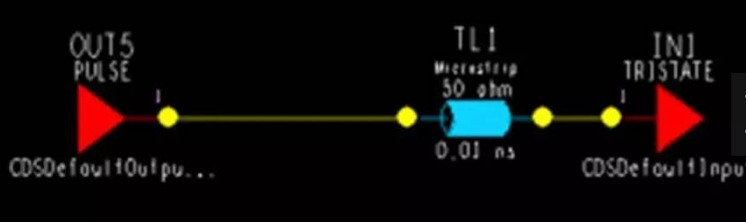

從上面的仿真結果看,源端內阻抗和傳輸線阻抗不匹配的確造成的反射,產生了過沖并生成了振鈴,這時我們就猜想這一切的產生是否和傳輸線的長度有關系呢?下面修改傳輸線延時為0.01ns。

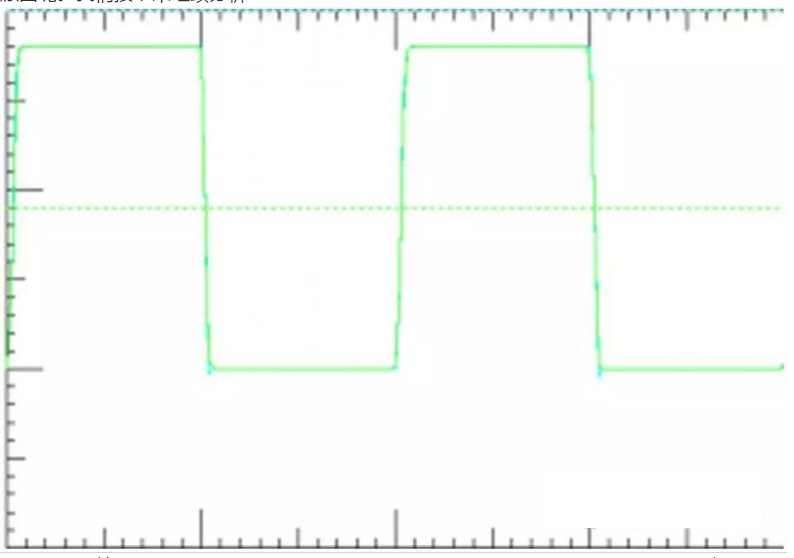

仿真頻率仍然為50Mhz看下仿真波形,驚訝地看到那些毛刺不見了,接收端和驅動端的波形接近重合,似乎沒有發生一點變形。

到這里有人也許會下這樣的結論,傳輸線足夠短的時候,就不發生反射了。那么這種論斷正確么?從反射的經典理論來看這個論斷是不正確的,因為理論中提到:只要信號探測到的阻抗發生變化,那么就會發生反射。理論和我們實際從表面上看似乎是發生了沖突,那么究竟是什么原因呢。我們接下來繼續分析…

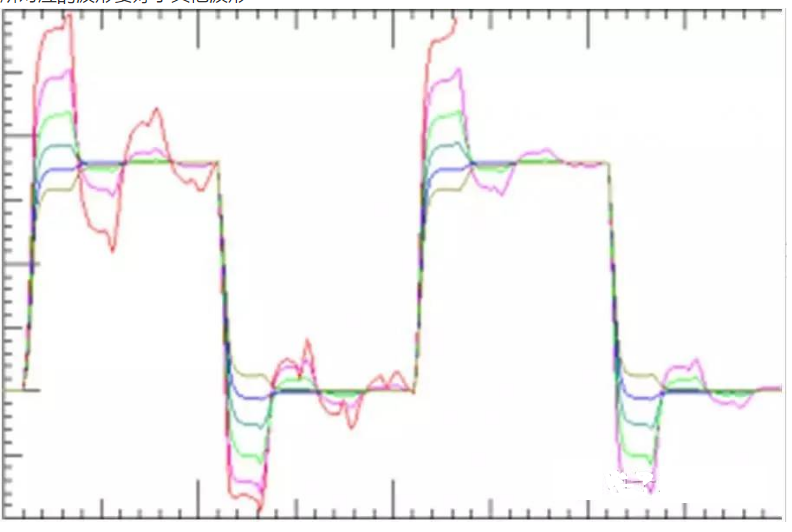

先不急著下結論,按照反射的經典理論為指導依據來處理反射問題,把傳輸線的延時改為1ns,在源端添加串聯電阻,阻值為0~50ohm,10ohm為步進進行掃描仿真。

紅色波形所對應的串阻阻值為0ohm,往下依次遞增,從接收端波形上看,這組取值中40ohm所對應的波形要好于其他波形

將40ohm對應的波形取出來單獨分析,從波形上看,接收端的波形比較好,而驅動端的波形有一個明顯的階梯狀,形成這個階梯狀的原因是什么呢?

為了便于分析驅動端波形發生了階梯狀,我們換一種仿真工具

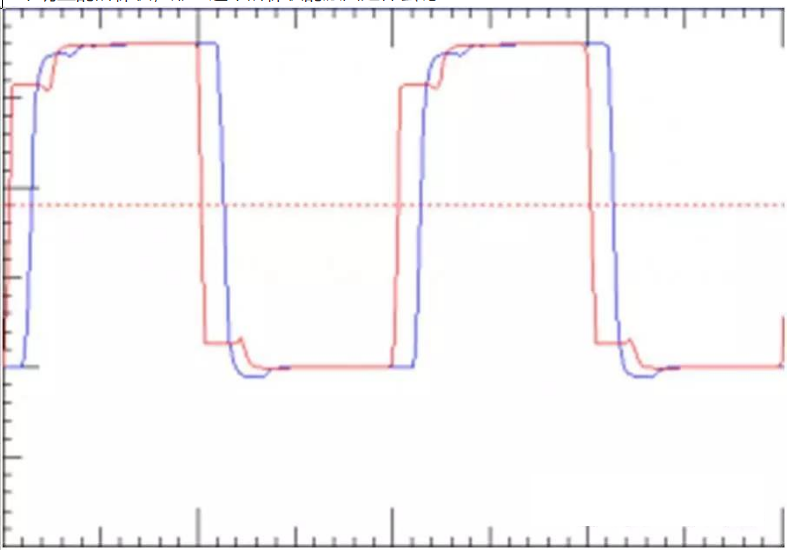

Hyperlynx,它可以設置探針測試點,更方便我們分析問題。我們在拓撲結構上選擇了4個測試點,其中紅色和紫色箭頭所指的波形應該是完全一致的,主要就是想看一下黃色箭頭處的波形和接收端的波形之間的關系。

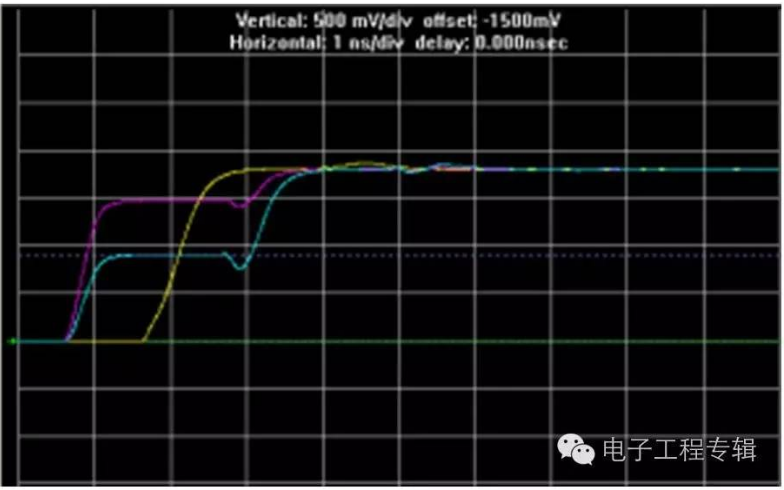

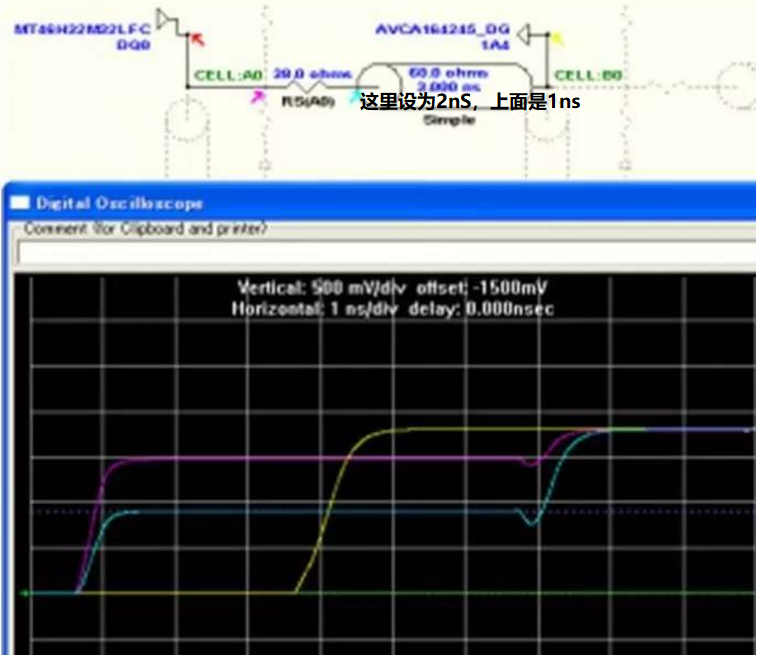

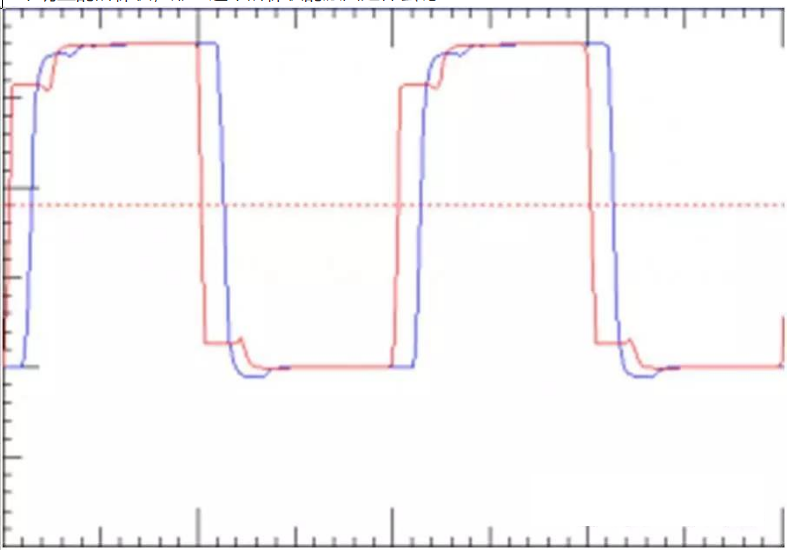

仿真頻率為50Mhz,傳輸線特征阻抗為60ohm,傳輸延時為1ns,仿真波形如下。青色波形呈現出明顯的半階梯形狀,圖中看到階梯維持在0.9V位置大約2ns左右,因為源端必須等待接收端的反射波回來后才能達到滿擺幅電壓,等待的時間是2倍的傳輸延時(1ns)。

相對于信號上升時間,傳輸延時越長,這里的階梯持續時間就越久。如下圖所示:

接下來分析一下這里的幾個波形,青色和紫色波形都出現了階梯。我們可能會有一個很不解的地方,就是為什么紫色波形出現的階梯那么的不可捉摸,有點怪怪的,其實它和青色波形產生的機理是一樣,而我們在SiXplorer中仿真,然后在Sigwave中看到的波形就是這里的紫色和黃色波形,沒有青色波形。所以習慣使用SQ的同志對驅動端波形出現的階梯可能會有不解的情況,在這里應該至少有一個感性的認識。

我們假定這里的驅動端源電阻和串聯電阻之和等于傳輸線的阻抗,那么信號傳播到串阻和傳輸線的分界點處,首先感受到的阻抗沒有變化,沒有發生反射,但是要分壓,真正進入傳輸線的電壓為信號電壓的一半(串聯分壓),注意這里說的是信號電壓,而不是驅動端的電壓,這兩者還是有區別的。

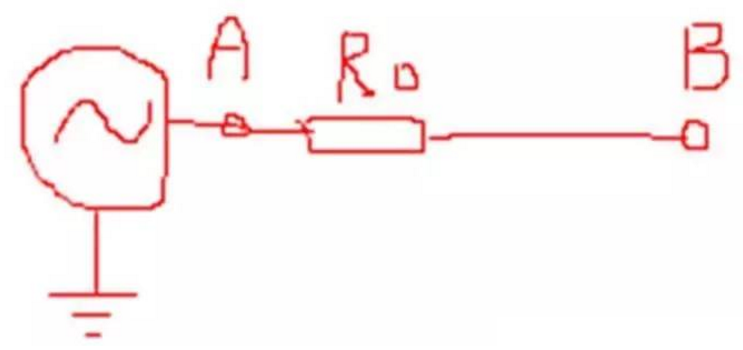

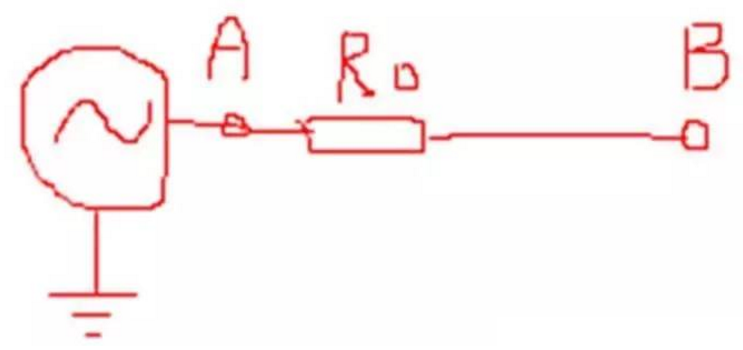

驅動端的等效電路如下:

其中R0是驅動端的內阻,這里的A點才是信號電壓,B點其實是驅動端的輸出電壓,而仿真出現的不可捉摸的階梯波形其實是B點的波形,形成機理和黃色波形一樣,但由于源電阻較小,所以此處的分壓(即紫色波形的階梯處電壓)應該為V=Vi*(Rs+Z0)/(R0+Rs+Z0) 其中Vi為信號電壓,R0為源內阻,Rs為串聯電阻,Z0為傳輸線阻抗代入值計算的V=1.8×(60+38)/(22+60+38)=1.47V,與仿真波形基本吻合

本站內容為本站編輯或整理,所以轉載務必通知本站并以超鏈接形式注明內容來自本站,以免帶來不必要麻煩。http://www.360doc.com/content/16/0524/12/32960231_561864778.shtml