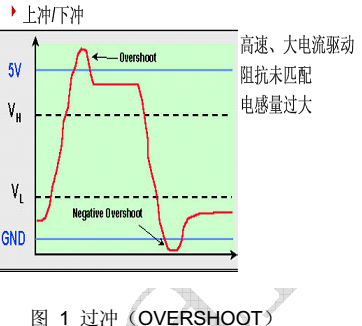

一、過沖:

1、過沖成因:

當較快的信號沿驅動一段較長的走線,而走線上沒有有效的匹配時,往往會產生過沖。

2、危害:

過沖帶來的問題主要是信號高電平“1”超出接收端器件的輸入最大電壓值,或者信號低電平“0”低于接收端器件的輸入最低電壓值。

3、解決方法:

對付過沖的一般方法是匹配,或叫端接(termination)。端接可總結為兩種形式:遠端串聯匹配消除二次反射,終端并聯匹配消除一次反射。注意不是每種方式都適用于任何場合。例如50ohm并聯匹配一般不適用與LVTTL/LVCMOS電平邏輯,因為電阻上消耗的功率很大。

減少過沖的另一方法是,減少驅動端的驅動電流。

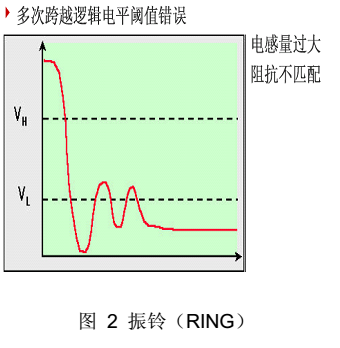

二、振鈴(ring)

過沖往往伴隨著振鈴,或者說過沖是振鈴的一部分。振鈴產生的第一次峰值電壓就是過沖。

振鈴的危害除了過沖之外,其產生 的電壓波動可能多次跨越邏輯電平的閾值電壓,導致接收端誤判。對于COMS器件,振鈴可能導致上、下MOS管同時導通時間過長,急劇增加器件功耗。

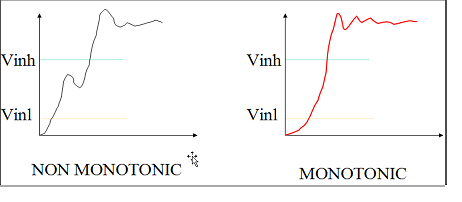

三、非單調性(non monotonic)

絕大多數非單調性都是由復雜的信號拓撲造成的。在一個CPU或DSP的本地總線上,非單調性問題最常見。

非單調性按表現形式可以分為兩種:回鉤和臺階。

對于一個沿有效的時鐘來說,信號沿上的回鉤和臺階是致命的。因為一個非單調性的時鐘沿,可能被接收端認作多個有效沿,或在器件內部產生亞穩態,導致時序邏輯的功能錯誤。對于數據來說,非單調性的危害主要是造成時間裕量的減少,這也是復雜的總線系統往往需要進行時序仿真的原因之一。

版權*轉載申明:

本站內容為本站編輯或整理,所以轉載務必通知本站并以超鏈接形式注明內容來自本站,以免帶來不必要麻煩。引文出處:https://blog.csdn.net/huanzx/article/details/73295310