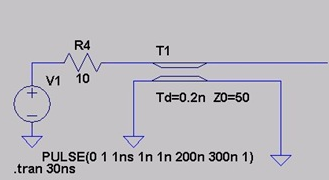

一般來(lái)說(shuō),當(dāng)傳輸線很短時(shí),傳輸延時(shí)在一定的范圍內(nèi),此時(shí)雖然仍然存在反射,但反射的波形在信號(hào)的上升沿之內(nèi),則從波形看,沒(méi)有大的影響,但究竟傳輸延時(shí)短到什么程度才算短呢?我們做一個(gè)實(shí)驗(yàn),還是通過(guò)spice仿真得到結(jié)果。圖1為仿真電路圖,該信號(hào)源端上升時(shí)間為1ns,幅度為1V,阻抗為10歐姆。

圖1 仿真電路圖

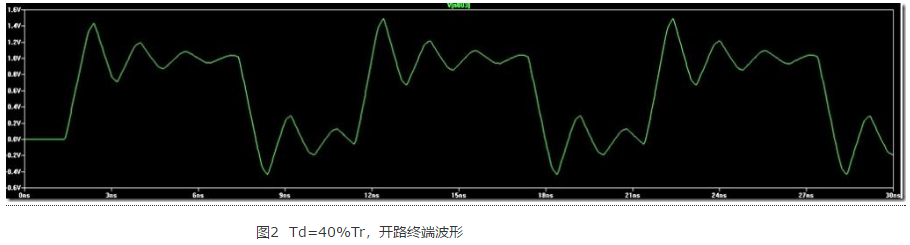

1、Td=40%Tr(Tr為上升時(shí)間,Td為傳輸延時(shí)),開(kāi)路終端波形。

圖2 Td=40%Tr,開(kāi)路終端波形

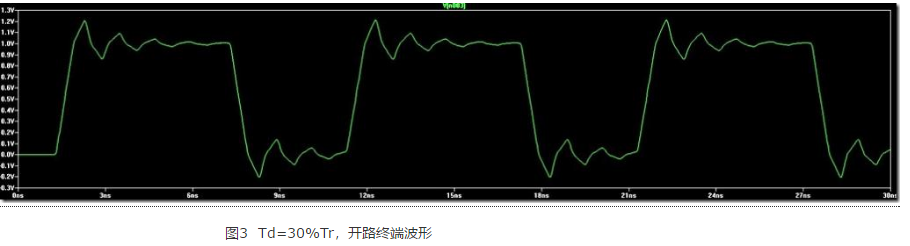

2、Td=30%Tr(Tr為上升時(shí)間,Td為傳輸延時(shí)),開(kāi)路終端波形。

圖3 Td=30%Tr,開(kāi)路終端波形

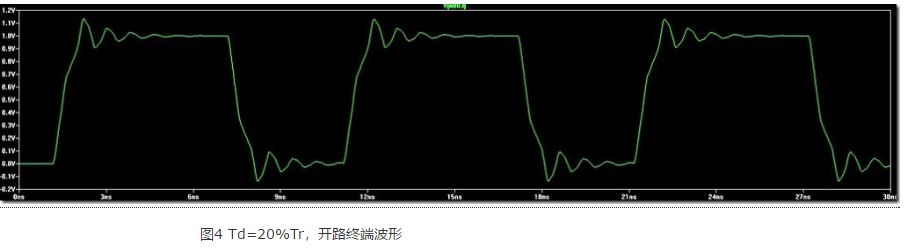

3、Td=20%Tr(Tr為上升時(shí)間,Td為傳輸延時(shí)),開(kāi)路終端波形。此時(shí)的過(guò)沖約為0.11V,為信號(hào)幅度的11%。

圖4 Td=20%Tr,開(kāi)路終端波形

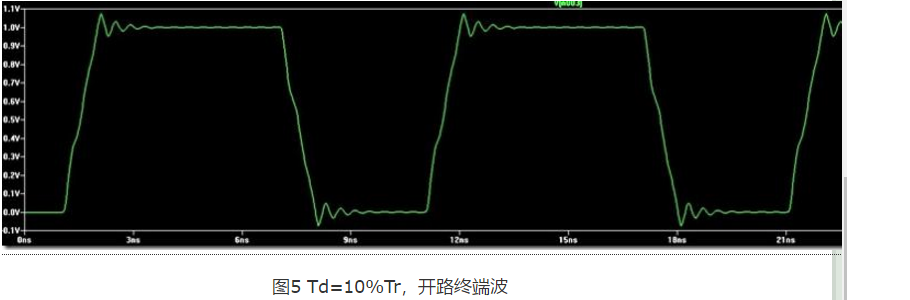

4、Td=10%Tr(Tr為上升時(shí)間,Td為傳輸延時(shí)),開(kāi)路終端波形。

圖5 Td=10%Tr,開(kāi)路終端波

由仿真可知,信號(hào)的過(guò)沖和傳輸線的時(shí)延有關(guān),《信號(hào)完整性分析》中描述說(shuō),“當(dāng)傳輸線延時(shí)Td>信號(hào)上升時(shí)間的20%時(shí),就要開(kāi)始考慮由于導(dǎo)線沒(méi)有終端端接而產(chǎn)生的振鈴噪聲。當(dāng)時(shí)延大于上升時(shí)間的20%時(shí),振鈴會(huì)影響電路功能,,必須加以控制,否則這是造成信號(hào)完整性問(wèn)題的隱患。吐過(guò)Td<20%信號(hào)的上升時(shí)間,振鈴噪聲可以忽略,傳輸線不需要終端匹配。”

所以,又出現(xiàn)了無(wú)敵的經(jīng)驗(yàn)法則:為了避免信號(hào)完整性問(wèn)題,沒(méi)有端接的傳輸線的最大長(zhǎng)度為,Len < Tr(Tr表示信號(hào)上升時(shí)間,Len的單位為in)。換算成mil就是乘個(gè)1000——是否進(jìn)行阻抗匹配端接阻容依據(jù)。

很悲劇的是,在目前的高速電路中,信號(hào)的上升時(shí)間已經(jīng)小于0.25ns,所以Len為0.25in(=6.35cm),一般來(lái)說(shuō),PCB上走線的距離很容易大于這個(gè)值,所以,必須對(duì)電路進(jìn)行端接設(shè)計(jì),同理1ns的上升時(shí)間,當(dāng)線長(zhǎng)超過(guò)1in=25.4cm時(shí)就需要加串聯(lián)電阻進(jìn)行阻抗匹配。

版權(quán)*轉(zhuǎn)載申明:

本站內(nèi)容為本站編輯或整理,所以轉(zhuǎn)載務(wù)必通知本站并以超鏈接形式注明內(nèi)容來(lái)自本站,以免帶來(lái)不必要麻煩。引文出處:https://www.cnblogs.com/chenman/p/3643698.html