一:前言

隨著PCB 系統的向著高密度和高速度的趨勢不斷的發展,電源的完整性問題,信號的完整性問題(SI),以及EMI,EMC 的問題越來越突出,嚴重的影響了系統的性能甚至功能的實現。所謂高速并沒有確切的定義,當然并不單單指時鐘的速度,還包括數字系統上升沿及下降沿的跳變的速度,跳變的速度越快,上升和下降的時間越短,信號的高次諧波分量越豐富,當然就越容易引起SI,EMC,EMI 的問題。本文根據以往的一些經驗在以下幾個方面對高速PCB 的設計提出一些看法,希望對各位同事能有所幫助。

1、電源在系統設計中的重要性

2、不同傳輸線路的設計規則

3、電磁干擾的產生以及避免措施

二:電源的完整性

1. 供電電壓的壓降問題。

隨著芯片工藝的提高,芯片的內核電壓及IO 電壓越來越小,但功耗還是很大,所以電流有上升的趨勢。在內核及電壓比較高,功耗不是很大的系統中,電壓壓降問題也許不是很突出,但如果內核電壓比較小,功耗又比較大的情況下,電源路徑上的哪怕是0.1V的壓降都是不允許的,比如說ADI 公司的TS201 內核電壓只有1.2V,內核供電電流要2.68A,如果路徑上有0.1 歐姆的電阻,電壓將會有0.268V 的壓降,這么大的壓降會使芯片工作不正常。如何盡量減小路徑上的壓降呢?解決壓降幾種方法:

a:盡量保證電源路徑的暢通,減小路徑上的阻抗,包括熱焊盤的連接方式,應該盡量的保持電流的暢通,如下圖1 和圖2 的比較,很明顯圖2 中選擇的熱焊盤要強于圖1。

b:盡量增加大電流層的銅厚,最好能鋪設兩層同一網絡的電源,以保證大電流能順利的流過,避免產生過大的壓降,關于電流大小和所流經銅厚的關系可參考本站其他文章。

2. 同步開關噪聲的問題。

同步開關噪聲(Simultaneous Switch Noise,簡稱SSN)是指當器件處于開關狀態,產生瞬間變化的電流(di/dt),在經過回流途徑上存在的電感時,形成交流壓降,從而引起噪聲,所以也稱為Δi 噪聲。開關速度越快,瞬間電流變化越顯著,電流回路上的電感越大,則產生的SSN 越嚴重。基本公式為:

VSSN=N·LLoop·(dI/dt) 公式1。

其中I 指單個開關輸出的電流,N 是同時開關的驅動端數目,LLoop為整個回流路徑上的電感,而VSSN就是同步開關噪聲的大小。

如果是由于封裝電感而引起地平面的波動,造成芯片地和系統地不一致,芯片的地被抬高這種現象我們稱為地彈(Groundbounce)。同樣,如果是由于封裝電感引起的芯片和系統電源被降低,就稱為電源反彈(PowerBounce)。如果芯片內部多個驅動同時開關時,會造成很大的芯片電源電壓的壓降和地平面的抬高,從而造成芯片的驅動能力的降低,電路速度會減慢。由公式1 可知減小回路電感可以減小VSSN,其中回路電感包括芯片管腳的寄生電感,芯片內部電源和芯片內部地的電感,系統的電源和地的電感,以及信號線自身的電感,這四部分組成。所以減小VSSN 的辦法主要有以下幾種方式。

a : 降低芯片內部驅動器的開關速率和同時開關的數目,以減小di/dt,不過這種方式不現實,因為電路設計的方向就是更快,更密。

b : 降低系統供給電源的電感,高速電路設計中要求使用單獨的電源層,并讓電源層和地平面盡量接近。

c :降低芯片封裝中的電源和地管腳的電感,比如增加電源/地的管腳數目,減短引線長度,盡可能采用大面積鋪銅。

d :增加電源和地的互相耦合電感也可以減小回路總的電感,因此要讓電源和地的管腳成對分布,并盡量靠近。

3. 地的分割原則

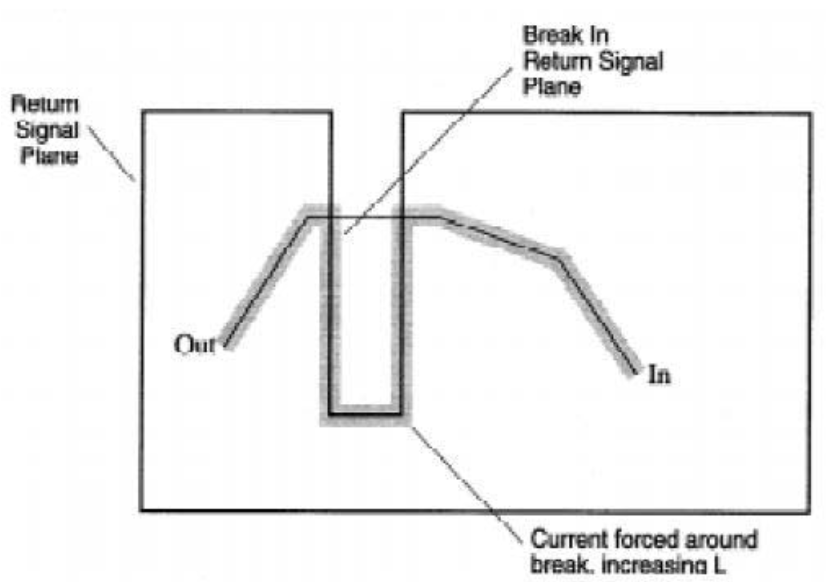

任何一根信號線中的電流都要通過和它臨近的地平面來回到它的驅動端,所以我們進行地的分割的時候要避免避免割斷高速信號的回留路徑,如下圖3 所示:

(圖3)

上面的信號回路的電流不得不繞過分割槽,這樣會產生很多相關的EMI 問題,以及會給信號線的阻抗匹配產生影響。

三:不同傳輸線路的設計規則

根據信號線所處印制版中的層疊位置可以將信號線分為微帶線和帶狀線,其中微帶線是指在PCB 的表層所走的線,有一層介質和它相臨,信號傳輸速度較帶狀線要快,帶狀線在PCB 的內層,有兩層介質相臨,信號傳輸速度比微帶線要慢,但是EMI,EMC 以及串擾等性能要好的多,所以建議高速信號都走成帶狀線。

根據信號控制。下面分別對影響單端線和差分線性能的因素進行一下分析。

1. 單端線反射的形成以及消除辦法

我們知道如果源端的阻抗和終端的阻抗相匹配那么信號的功率將會是最大,如果終端和源端阻抗不匹配則將會引起信號的反射,部分信號還會輻射出去造成EMI 問題。

(圖4)

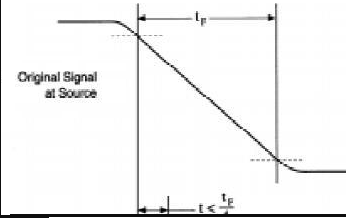

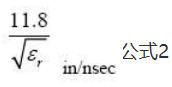

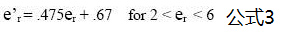

那么什么時候反射不用考慮,什么時候不得不考慮呢?如圖4所示,假設信號從源端由高電平變為低電平傳輸出去,信號傳輸延時為Tp,(有的文檔將沿跳變時間<=四分之一Tp 做為把信號線看成微波中傳輸線的條件)如果2Tp 小于信號沿的跳邊時間的話,反射因素就不用考慮,因為不會影響電平的判斷,只會使沿的跳變不規則。相反的如果2Tp 大于信號沿跳變的時間,那么反射會在發射端形成振鈴現象,會影響到電平的判斷,所以要考慮影響。(可參見本站文章:“信號的上升時間和傳輸延時”)信號線在介質中的傳輸速度為:

公式2 為信號線為帶狀線時的傳輸公式。當信號線為微帶線時,傳輸的介電常數的計算公式為:

如果信號線過長則反射因素就不得不考慮。反射的解決的辦法可以在線上串一個小歐姆阻值的電阻,還可以并一個小容值的電容,不過這種方法不太現實。

2. 影響信號間串擾的因素及解決辦法。

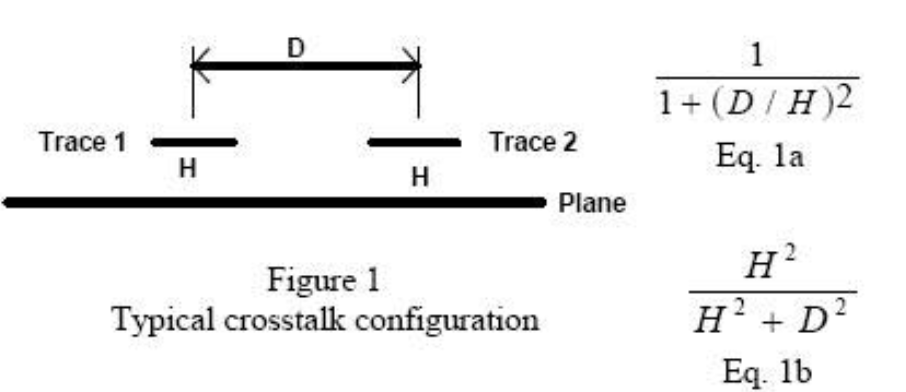

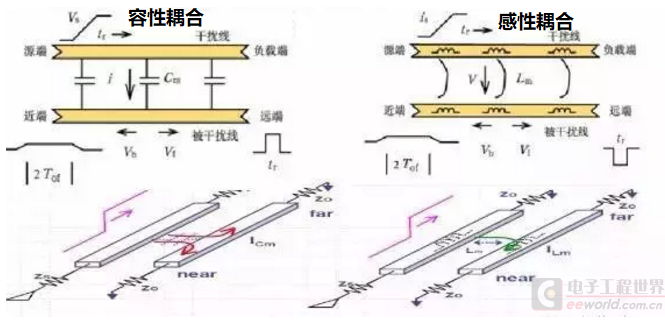

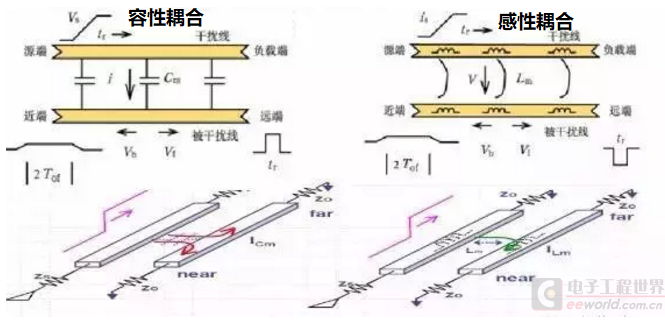

串擾是信號傳輸中常見的問題,串擾是由電磁耦合引起的,耦合分為容性耦合和感性耦合兩種。有些說法只要控制間距是線寬的3 倍就可以了,也就是常說的3W 原則,這種說法只是說間距越大越好,但還是不夠全面。

(圖7)

由圖7 可知除了和線間距D 有關,還和走線層和參考平面的高度H有關。D 越大越好,H 越小越好。隨著PCB 的密度越來越高,有時候不能滿足3W 原則,這就要根據系統的實際情況,看多大的串擾能夠忍受,另外由于工藝的原因H 也不能太小,一般都不要小于5mil;串擾解決辦法:增加線間距,縮小信號與參考平面距離。

減小感性耦合的關鍵是減小騷擾源和敏感對象之間的互電感。從磁場強度的角度來說,主要是降低敏感對象周圍空間的磁感應強度。一般而言,抑制感性耦合要比抑制容性耦合困難。實際中應用的主要方法和措施有:

①增加騷擾源和敏感對象之間的距離。

②調整騷擾源和敏感對象的方位,如在電子電路中,通過調整電源變壓器和輸出變壓器的鐵芯方位使其相互垂直,從而減小電源變壓器對輸出變壓器的磁場耦合。

③采用磁屏蔽措施,在騷擾源和敏感對象之間插入高導磁材料、如將電纜放入鐵管中,利用鐵管的高導磁特性屏蔽騷擾源磁場對電纜的影響。

④采用電磁屏蔽措施,在騷擾源和敏感對象之間插入導電材料,利用外部變化磁場在導電材料中感生的渦流場所產生的反向磁場來抑制在敏感對象周圍空間產生的合成磁場。

⑤

減小騷擾源和敏感對象回路的有效面積,進而減小互電感。

減小容性耦合的關鍵是減小騷擾源和敏感對象之間的互電容。從電場強度的角度來說,主要是降低敏感對象周圍空間的電場強度。應用的主要方法和措施有:

①增加騷擾源和敏感對象之間的距離;

②采用靜電屏蔽措施,在騷擾源和敏感對象之間插入導電材料。在實際中,針對不同情況采用的靜電屏蔽措施也不相同。主要有:

①盡可能地使用屏蔽電纜或將未加屏蔽的電纜放到金屬管或金屬槽中;

②將敏感對象放到金屬屏蔽盒或屏蔽室內;

③將敏感對象放到經過金屬鍍膜的塑料屏蔽盒內;

④對于傳輸線,可以在產生騷擾的傳輸線和敏感傳輸線之間鋪設單端或雙端接地的金屬屏蔽線。

3. 差分線阻抗匹配和走線應注意事項

現今LVDS 走線越來越流行,主要原因是因為它是采用一對線對一個信號進行傳輸,其中一根上傳輸正信號,另一根上傳輸相反的電平,在接收端相減,這樣可以把走線上的共模噪聲消除。另外就是因為它的低功耗,LVDS 一般都采用電流驅動,電壓幅度才350mvpp。 當然它也有缺點就是需要2 倍寬度的走線數來傳輸數據。

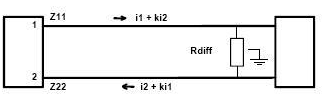

差分線一般傳輸信號的速度都比較快,所以要進行嚴格的阻抗控制,一般都控制在100 歐姆。下圖10 為一個差分傳輸模型,其中Z11和Z22 分別為兩跟信號線的特性阻抗,K 為另外一跟線對自己的耦合系數。I 為線上的電流。

圖10

1 線上任意一點的電壓為V1=Z11*i1+Z11*i1*K, 2 線上任意一點的電壓為 V2=Z22*i2+Z22*i2*K 因為Z11=Z22=Z0,i1=-i2,所以V1 和V2 大小相等方向相反。所以差分阻抗為

Zdiff=2*Z0*(1-K) 公式4

由公式4 可知差分阻抗不僅和單跟線的特性阻抗Z0 有關,還和耦合系數K 有關,所以調整線寬,間距,介電常數,電介質厚度,都會影響到差分阻抗。

另外差分線大多應用在源同步時鐘系統當中,這就要求數據線和時鐘線的長度要匹配,類外由差分線自身的特性要求一對之間的兩跟線要匹配。下圖11 為等長的理想的差分線在接收端的情形。可以看到兩跟線完全等延時,再相減之后不會出現誤碼。而圖12 為其中一跟線的延時比另一跟要長的情形,這樣再相減誤碼很容易產生。

由于布線工具和器件本身以及工藝的原因很難做到每一對線和對與對之間的線都匹配,至于相差多少合適,并沒有嚴格的公式,即使有也要具體情況具體分析,不可能都使用。根據以往的調試經驗當信號工作在500MHZ~~800MHZ 之間時,對內相差80mil,對間和時鐘相差+-250mil,不會出現問題。(僅做參考)。

四:電磁干擾的產生及避免措施

EMI 即電磁輻射是很常見的問題,主要減少電磁輻射的辦法有以下幾種方法:

a :屏蔽。在比較敏感或高速的信號周圍用地平面進行屏蔽,每格1000mil 打一個地孔。

b :避免或減小信號的環路面積。由電磁場理論可知變化的電場產生變化的磁場,當開關頻率很高的時候,會由環路向外輻射電磁能量,也容易接收外面的磁場,就象是一個天線,所以應該盡量避免。

c :做好電源的濾波。濾波的器件主要包括磁珠和電容。磁珠類似帶通濾波器,可以抑制高頻,選擇不同容值的電容可以針對不同頻率的濾波起到旁路作用。

版權*轉載申明:

本站內容為本站編輯或整理,所以轉載務必通知本站并以超鏈接形式注明內容來自本站,以免帶來不必要麻煩。引文出處:http://www.360doc.com/content/12/0412/22/584129_203147596.shtml